how dare you Im not an engineer

What language is that engineer and a nerd one?

Matlab.

R

We can reject the null hypothesis that you are not a nerd at significance $\alpha < 0.001$.

oh wait, shit let me run that again, my data frame is full of NA somehow, again.

Laughs in perl

TMTOWTDI.

Nerd.

It’s dark… you are eaten by a grue.

No. The proper term is GEEK. Needs are uncoordinated, awkward, have no fashion sense, and occasionally tape their broken glasses (or say sheepishly, “did I do that?”)

Geeks have in-depth, we’ll researched knowledge on topics that are obscure to the “mundanes”, have intellectual curiosity, and sometimes gain in wealth as a result. In many cases, they tend to make non-geeks (and geeks for other topics) completely befuddled. This sometimes results in insecurity on the part of non-geeks, which negatively impacts their social lives. On rare occasions, such geeks are so over the top smart that they transcend such petty attitudes (see: Neil deGrasse Tyson)

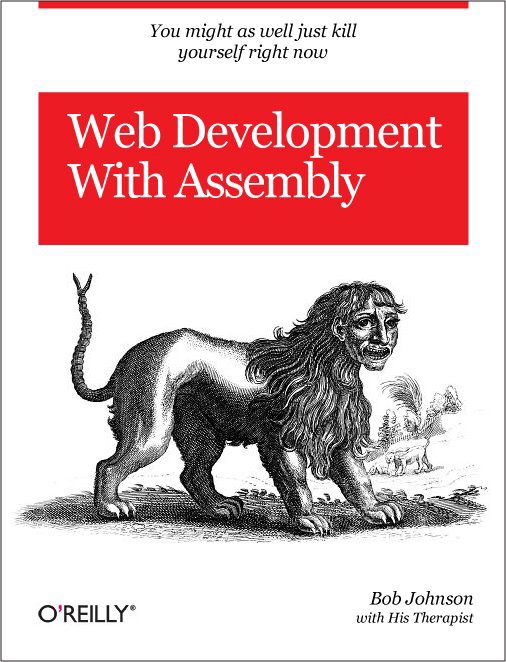

If you’re programming in assembly, regardless of what it is, you are the biggest nerd of them all. And I have massive fucking respect for you.

Wow I’m an old engineer nerd. I feel so exposed. Zero is nothing always start at one for life.

…but some nerds are more equal than others.

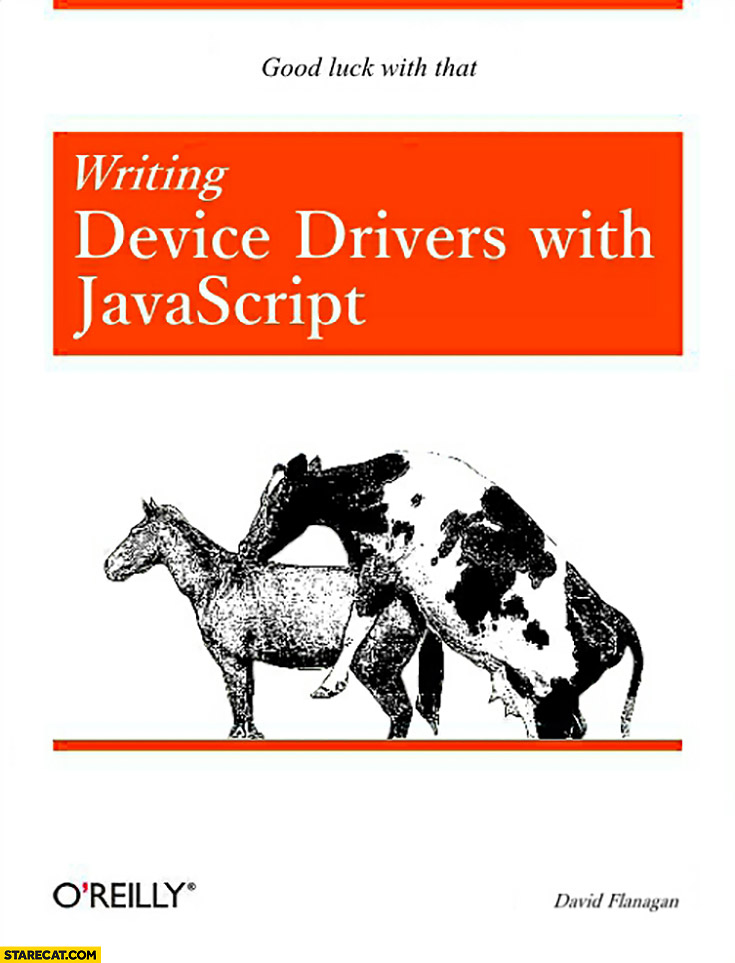

Javascript should say “you are a masochist and a nerd”

Who thought of that and how have they managed to sustain their core bodily functions this long?

Probably this guy

I take it that he dictated the book to his therapist from a state of paralysis.

That should be a dog fucking a football.

🤓

I am not in this chart because my favourite programming languages are too nerdy for the cool programming nerds to include in their nerd chart.

Super nerd

Nerd.

Fair.

Same here.

VHDL represent. Although it’s arguably not a “programming language”

You work at IBM or something? Who even still uses VHDL?

I do mostly c/c++ for an embedded product, but one of the modules in the system uses an FPGA programmed w/ VHDL. So I’ve gotten to do a few deep dives into that code in the past couple years.

It’s been decades since I’ve had to write new VHDL or Verilog though.

A ton of people. Anything aerospace, DoD, Space, or critical infrastructure. All those industries have to use VHDL to support legacy products from the 80s and 90s. At that point everyone is like, “Sure its 2025, by why switch to SystemVerilog? We already know VHDL.” and thus you got a whole army of engineers making next gen satellites, augmented reality headsets, etc. …… in VHDL 93.

Is it such a hassle learning verilog if you know vhdl or vice versa?

Not really, HDL is HDL. At the end of the day, as long as you know what you want to do electrically then everything else is an exercise of translating that desire into VHDL, Verilog, or SystemVerilog. The only real hassle is creating test-benches and verification simulations. But at that point it’s discretionary towards the designer. A lot of tools coming from Intel, Xilinx, and Synopsys allow you to “black box” components. So a module written in VHDL can be incorporated into a design or test bench written in verilog and vis-versa. IMHO VHDL is still dominant because grey beard chief engineers throw a little hissy fit at design reviews when they learn the junior engineers did everything in verilog.

Tbf, I am not a grey beard chief engineer, and I strongly prefer VHDL for design. For verification I actually really like SystemVerilog.

VHDL is strongly types, which prevents a lot of issues with types that I’ve hit with [System]Verilog.

Also, having learned VHDL first, I think it is easier to go from VHDL to Verilog, as opposed to vice versa. And this is mainly because VHDL is stricter.

Lol, so much of the FPGA industry 🤣. Especially East coast of the US

Perl should say: You are old and a nerd or you use Debian

what about BASIC